인공지능 연산의 폭발적 증가로 전력과 냉각 자원의 부담이 커지고 있다. 이럴 때일수록 더 낮은 전력으로 더 높은 성능을 내는 소자·집적 기술이 중요하다. 현재 많은 연구자들이 그 해답을 이차원(2D) 반도체에서 찾고 있다. 이차원 재료는 원자 수 층으로 얇고 계면이 깨끗해 누설전류와 높은 전하 이동도를 가지면서도, 낮은 공정 온도에서 이종기판 위에 높은 결정성을 가지도록 직접 성장할 수 있다. 결과적으로 개별 소자의 지속적 스케일링(More Moore)과, 센서·메모리·뉴로모픽 등 다기능 소자의 통합(More than Moore)을 한 플랫폼에서 동시에 추구할 수 있는 토대를 제공한다.

[그림 1]. 이차원 반도체의 M3D 집적(서울대학교 재료공학부 이관형 교수 제공)

왜 지금 2D 반도체인가?

실리콘 트랜지스터는 채널이 수 nm대로 얇아질수록 표면 결함에 의한 전하 이동도 저하가 점점 커진다. 반면 이차원 반도체는 Dangling bond가 없는 원자층 구조 덕분에 초박형에서도 실리콘 대비 이동도 저하가 완만하고, 저유전 상수·큰 밴드갭으로 누설전류 억제에 유리하다. 더구나 저온 성장(< 400 °C)의 잠재력과 유전체 위 단결정 성장 가능성은 모놀리식 3D(M3D) 집적에 필수적이다.

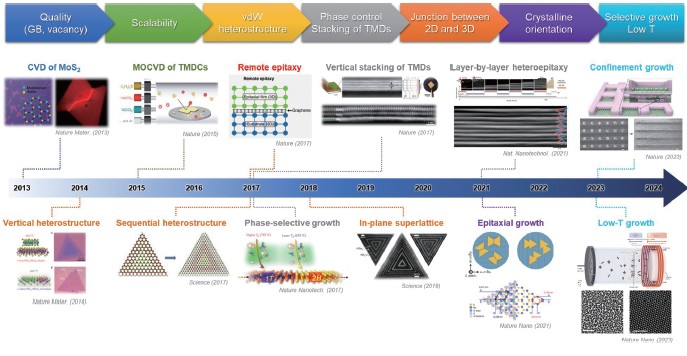

합성 로드맵: CVD/MOCVD부터 vdW epitaxy에서 hypotaxy까지

이차원 반도체의 합성 또는 증착은 분말을 증발시켜 합성하는 화학기상증착법(Chemical Vapor Deposition, CVD), 금속박막의 칼코겐화를 통한 합성, 금속유기 화학기상증착법(Metal-Organic CVD, MOCVD) 등을 사용하고 있다. 이 기술은 각각 대면적·두께 제어형 합성에서 장단점을 가지고 있으며, 현재는 선택적 공급에 기반한 이종 에피택시(동일 기판에서 수직/수평 헤테로구조 구성이 가능)까지 가능한 수준으로 발전했다. 특히 가스 전구체를 쓰는 MOCVD는 웨이퍼 스케일 균일성과 상대적으로 낮은 합성 온도(150 ~ 400°C)가 강점이다.

[그림 2]. 이차원 반도체 합성 기술의 발전 동향(서울대학교 재료공학부 이관형 교수 제공)

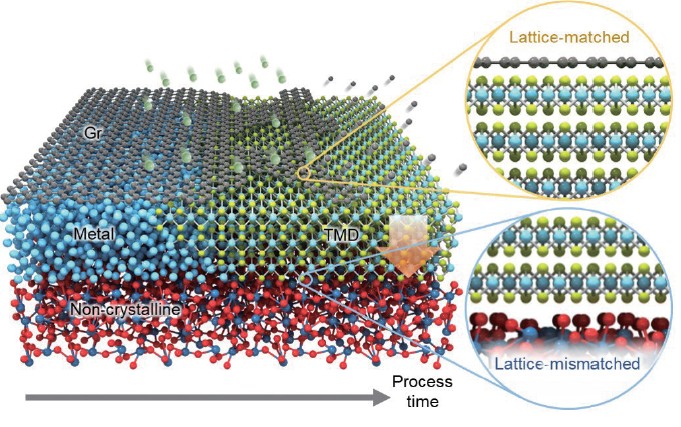

‘하이포택시(Hypotaxy)’: 전사 없는 단결정 박막 합성으로 가는 길

최근에는 우리 연구실은 그래핀의 나노포어를 매개로 한 이차원 반도체 물질의 단결정 성장 기술인 하이포택시(Hypotaxy)가 개발하여 Nature지에 보고하였다. 핵심은 그래핀과 같은 2D 템플릿의 나노포어를 통해 아래 방향으로 단결정 이차원 반도체 층이 자라면서도 템플릿과 반데르발스 결정 정합을 유지하는 성장 메커니즘이다. 나노포어 크기가 5 nm보다 작을 때는 핵 생성이 나노포어 당 한 개로 제한되어 결정 정합이 유지되고, 그보다 크면 여러 방향으로 정렬된 다수의 핵이 생긴다. 따라서 그래핀의 나노포어를 정밀하게 제어하면 단결정으로 정렬된 이차원 반도체 물질의 두께 제어가 가능한 형태로 합성이 가능하고, 공정 중 그래핀이 자연스럽게 제거되어 매우 깨끗한 표면의 단결정 이차원 반도체를 얻을 수 있다.

이를 통해 4인치 웨이퍼 크기로 이차원 반도체의 단결정을 합성할 수 있으며, 높은 균일성, 낮은 결함밀도의 우수한 특성을 확보할 수 있으며, 특히 M3D 집적의 필수조건인 낮은 온도(< 400 °C)에서의 합성이 가능함을 증명하였다. TDTR을 이용한 열전도 특성과 소자 어레이 제작을 통한 트랜지스터 특성을 평가한 결과, 높은 열전도도와 우수한 전하 이동도(89 cm²/V·s), 그리고 높은 점등비율(≈ 3×109) 등의 소자 지표을 얻을 수 있음을 보고하였다. 또한 하이포택시 방식은 유전체, 금속 등 다양한 기판 위에서 이차원 반도체의 단결정 성장을 가능하게 하여, BEOL 호환 M3D 집적의 병목을 푸는 실마리로 평가된다.

[그림 3]. 하이포택시 공정의 개념도(서울대학교 재료공학부 이관형 교수 제공)

모놀리식 3D 집적: ‘More Moore’와 ‘More than Moore’의 접점

전통적 실리콘은 상층 공정 온도(< 450 °C)의 제약과 비결정 기판 위에 증착할 경우 결정성의 손실이 발생하는 한계가 있었다. 이러한 면에서 이차원 반도체는 저온 직접 성장과 센서/메모리/뉴로모픽 디바이스의 기능 통합 가능성을 근거로, M3D에서의 다기능 집적 경로를 제시할 수 있다. 이는 연산-메모리 결합(in-Memory Computing), 바이오·옵토센싱 등 비폰노이만 소자와도 맞닿아 있다.

소자 공정의 관건: 접촉·유전체·저손상 금속화

하지만 이차원 반도체의 산업적인 적용을 위해서는 여전히 금속-이차원 반도체 계면에서의 페르미 레벨 고정 현상(Fermi level pinning)을 완화하고, 금속의 일함수의 제어하고 손상 없는 금속화로 낮은 접촉저항을 확보해야 하며, 2D 표면 위 균일 고품질 산화막 증착 등의 이슈가 해결되어야 한다.

이차원 강유전: ‘슬라이딩’으로 여는 새로운 자유도

이차원 반도체는 단순히 실리콘의 공정적인 한계를 극복하는 것 뿐 아니라, 새로운 기능을 부여하여 새로운 소자의 개발도 가능케 한다. 예를 들어, 3R 구조를 가지는 이차원 반도체의 이중층은 반전대칭이 깨져 자발분극을 보이며, 층간 슬라이딩으로 분극 전환이 가능하다. 따라서 주기적 도메인(Periodic domain)과 완전 정합(Fully commensurate)의 대비, 전계–온도–구조 균질성이 보유력·잔류분극·내구성에 미치는 영향, 그리고 CVD 기반 구조 제어(프로모터 활용)에 따른 단일 도메인 구현 등의 연구를 진행하고 있다. 단일 도메인으로 이루어진 슬라이딩 강유전성을 가지는 이차원 반도체 이중층은 도메인 경계의 고정 현상이 없어 급격한 분극 전환이 가능하고 높은 Curie 온도(> 180 °C)의 안정성을 가지고 있어 강유전성을 가지는 반도체를 채널로 이용한 이차원 강유전성 반도체 전계효과 트랜지스터(2D Ferroelectric semiconductor Field-effect transistors, 2D FeSFETs)를 구현할 수 있어, 차세대 메모리 및 뉴로모픽 소자에 적용할 수 있는 큰 가능성을 보인다.

이차원 반도체의 응용과 전망

이차원 반도체의 초박형·저결함 채널은 전력 효율을 높이고, 메모리/센서/연산의 수직 적층으로 칩-간 통신 병목을 줄일 수 있다. 그리고 MOCVD, 하이포택시 등의 다양한 합성 기술과 자온 합성과 스케일 업을 위한 노력은 파운드리 공정의 호환성을 높이고 있다. 향후 과제는 균일 단결정 필름의 더 넓은 면적화, 변형·오염·정렬 오차 관리, 열·습도·기계적 안정성 검증, 그리고 산업표준 TCAD/컴팩트 모델 구축이 있다. 정리하면, 이차원 반도체는 소자 스케일링과 다기능 소자의 집적을 동시에 여는 실용 플랫폼으로 폭발적인 연구 단계에 들어섰고, 하이포택시와 저온 에피 성장의 진전이 현장 적용의 촉매가 될 것으로 보인다.

‘이차원 반도체의 다음 단계: 이차원 반도체의 합성과 모놀리식 3D 집적, 그리고 신소자 응용’에 관한 궁금한 내용은 본 원고 자료를 제공한 이관형 교수를 통하여 확인할 수 있다.

[사진 1]. 2025 스마트 사이언스 코리아 with KOREA LAB Autumn 특별강연 현장

Reference(참고문헌): Nature 625, 276–281 (2024) / Nat. Rev. Elec. Eng. 1, 300–316 (2024) / Nature 520, 656–660 (2015) / Nat. Nanotechnol. 16, 1092–1098 (2021) / Nat. Nanotechnol. 17, 33–38 (2022) / Nat. Nanotechnol. 18, 1289–1294 (2023)

The Person in Charge(발표자): 서울대학교 재료공학부 이관형 교수

e-mail: gwanlee@snu.ac.kr

<이 기사는 사이언스21 매거진 2025년 11월호에 게재 되었습니다.>